ETP4HPC Conference, Sassenheim (near Amsterdam), the Netherlands

From 13/02/2024 to 14/02/2024

13 February 12:00 to 14 February 2024 13:30

This second edition of the ETP4HPC Conference will take place again at the Van der Valk Hotel in Sassenheim-Leiden (near Amsterdam). Join us to meet the European HPC community, get the visions from our keynote speakers on the evolution of HPC, and exchange with the ETP4HPC members. The agenda includes ample time for networking, during lunches, breaks and Q&As.

This second edition of the ETP4HPC Conference will take place again at the Van der Valk Hotel in Sassenheim-Leiden (near Amsterdam). Join us to meet the European HPC community, get the visions from our keynote speakers on the evolution of HPC, and exchange with the ETP4HPC members. The agenda includes ample time for networking, during lunches, breaks and Q&As.

The ETP4HPC Conference is open to all - Registration is closed as of noon, Feb 5, 2024. Please contact the ETP4HPC Office for any urgent queries.

Agenda

13 February

- 12:00-13:00: Welcome buffet lunch

- 13:00-13:15: Opening & introducing our Guests (EUMaster4HPC Students)

- 13:15-14:00: Keynote 1 - Trust in the Era of Data Deluge (Damien Gratadour, Observatoire de Paris, Centre national de la recherche scientifique) followed by Q&A

- 14:00-14:30: Destination Earth’s ‘Federation’ White Paper (Utz-Uwe Haus, HPE & Craig Punty, SiPearl)

- 14:30-15:15: ETP4HPC 2.0 - Presentation of the new Vision for ETP4HPC (30’ presentation +15’ discussion, Jean-Pierre Panziera, ETP4HPC Chair & Marcin Ostasz, ETP4HPC Office)

- 15:15-16:00: Coffee break

- 16:00-16:15: ETP4HPC 2.0 - Wrap-Up

- 16:15-16:30: Presentation of New Members

- 16:30-17:00: Keynote 2 - Long-term Computing Vision (Jean-Yves Berthou, INRIA) - Talk Summary

- 17:00-17:30: KeyNote 3 - A Vision of Industrial HPC Use - Challenges, Opportunities and Obstacles (Stephan Schenk, BASF)

- 17:30-18:30: Disruptive Innovations - Giovanni Samaey (KU Luewen) - Time-X: time-parallel simulation tools in science and engineering & Manuel Arenza (Codee) - Automated code inspection for performance /please check the summaries below/

- 18:30-18:45: Conclusions (Jean-Pierre Panziera, ETP4HPC Chair)

- 19:30-21:00: Networking dinner

14 February

- 9:00-9:45: SRA 6 - Main Research Directions, Interaction with the RIAG/EuroHPC JU/EC, Collaboration with other Continuum areas (Sai Narasimhamurthy, ETP4HPC SRA 6 leader)

- 9:45-10:45: Parallel Sessions - SRA Working Groups presenting their progress:

- HW Working Groups - Moderator: Michael Malms: System Architecture, System Hardware Components, Non-Conventional Architectures, I/O and Storage, Ecosystem Technologies, Quantum+HPC (Thematic Trend), Federation (Thematic Trend)

- SW Working Groups - Moderator: Sai Narasimhamurthy: System Software and Management, Programming Environments, Maths and Algorithms, HPC Usage, Energy Efficiency (Thematic Trend), AI + Distributed Data Analytics (Thematic Trend)

- 10:45-11:15: Coffee break

- 11:15-12:15: KeyNote 4 - EC & EuroHPC JU, followed by a discussion: How to strengthen the liaison between ETP4HPC - RIAG - EuroHPC JU? (Anders Jensen, EuroHPC Executive Director; Panagiotis Tsarchopoulos, EC)

- 12:15-12:30: Closure

- 12:30-13:30: Farewell buffet lunch

Speakers

The Short Bios of the Speakers can be downloaded here.

- Amandine Samson - EUMaster4HPC Projectr Manager, Sorbonne Université, EUMaster4HPC

- Damien Gratadour - Senior Research Scientist at Observatoire de Paris, CNRS

- Utz-Uwe Haus - Head of Hewlett Packard Enterprise EMEA Research Lab

- Craig Prunty - SiPearl VP Marketing & Business Development

- Jean-Yves Berthou - Director of the Inria Saclay Research Center

- Dr. Stephan Schenk - Product Manager for High Performance Computing at BASF SE in Ludwigshafen, Germany

Call for Disruptive Innovations - summaries:

1 - Time-X: time-parallel simulation tools in science and engineering - Giovanni Samaey, KU Luewen, Coordinator of EuroHPC Time-X project - please check Giovanni's bio

To unlock the potential of the massive parallelism in current and future exascale systems, parallel-in-time (PinT) simulation has emerged as a powerful algorithmic paradigm to reduce the wall-clock time for time-critical applications. Since time integration is a typical sequential process, parallelization across the time dimension requires a fundamentally new algorithmic approach, and the changed communication patterns also require rethinking software implementations.

Recent breakthroughs in algorithm and software design have yielded significant reductions in scientific and engineering domains as diverse as computational medicine, drug design, weather and climate and electromagnetism. Open-source software libraries illustrate both how time-parallelism can be included as a non-intrusive wrapper around existing simulation codes, and serve as a guide to implement the methods into existing simulation software.

Still, while parallel-in-time simulation methods are gradually maturing, new challenges arise when combining these methods with next-generation methods for optimization, uncertainty quantification, and data assimilation. In addition, also the combination of physics-based simulation and machine learning techniques, as well as the use of parallel-in-time methods for training of deep neural networks, opens up pathways to significant computational breakthroughs.

In this talk, we will overview some recent successes and a roadmap for future developments that will allow to maximise the impact of this disruptive innovation.

Automated code inspection for performance - Manuel Arenaz Codee, CEO & Founder

The Codee technology brings a brand-new innovation in the space of software development tools. Appentra Solutions is a startup company headquartered in Spain with world-wide rights over the Codee technology, conceived and developed in Europe taking advantage of 10+ years of R&D at the University of A Coruña, the european projects MAESTRO, EPEEC and EuroHPC OPTIMA, and additional funds from European private investors. Today Codee is a mature technology powering Codee: The First Static Code Analyzer specialized in Performance, commercialized by Appentra in the HPC and embedded markets.

The novelty of Codee is a break-through, disruptive technology to address the fundamental problem of automated analysis of C/C++/Fortran source code, being complementary and not a replacement for LLVM software. Codee extracts “semantic source code features” (e.g. compute/memory/communication patterns, temporary variables, parallel loops), enabling the automation of new sophisticated code checkers. Codee provides a systematic, predictable, extensible approach with a huge development potential in the software development market.

The DevAI space is vibrant today, with many LLMs and Generative AI tools available. They are based on probabilities, do not guarantee correct reproducible results, and struggle to extract complex semantic features from the code (Sharma et al. 2022). We envision Codee technology helping to create (i) high-quality training sets for coding; (ii) conversational models for predictable coding; and (iii) AI Coding Assistants checking for code correctness.

Brainstorming and networking with ETP4HPC experts about ways of using Codee technology in the DevAI space would be highly valuable.

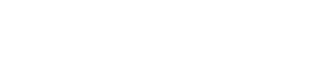

Thematic blocks of the agenda

The following are the thematic blocks of the Event’s Programme: there are three keynotes related to a technology vision, a discussion on the strategy of ETP4HPC, a block of keynotes and workshops on our Strategic Research Agenda 6 (SRA 6), and a Networking Dinner on the evening of Day 1. We expect the presence of representatives of the EuroHPC JU, its RIAG (Research) and INFRAG (Infrastructure) bodies, the EC, and other organisations across the Digital Continuum. The EUMaster4HPC project and its students will also be at the Event. A Call for Disruptive Innovations has been opened with a view to showcasing innovative pieces of technology at the Event.

- confirmedInternal ETP4HPC event

- to be confirmedInternal ETP4HPC event

- externalExternal organisation event