## ETP4HPC

European Technology Platform for High-Performance Computing

## Strategic Research Agenda 2015 Update

European Technology Multi-annual Roadmap Towards Exascale **Update to 2013 Roadmap**

SUPPORTED BY THE **EXDCI** PROJECT WITH FUNDING FROM THE EUROPEAN UNION'S HORIZON 2020 RESEARCH AND INNOVATION PROGRAMME UNDER THE GRANT AGREEMENT **NO 671558**  ETP4HPC is an industry-led think tank and advisory group of companies and research centres involved in High-Performance Computing (i.e. Supercomputing) technology research in Europe. It was formed in 2011 with the aim to build a world-class HPC Technology Supply Chain in Europe, increase the global share of European HPC and HPC technology vendors as well as maximise the benefit of HPC technology for the European HPC user community. ETP4HPC is also the EC's partner in the HPC contractual Public-Private Partnership (cPPP<sup>1</sup>) which monitors and manages the European HPC research investment programme supported by a €700M investment by the EC within the Horizon 2020 programme.

ETP4HPC believes that a competitive European HPC technology value chain will help Europe achieve economic leadership through the use of HPC tools for product creation and service delivery, for the development and supply of worldclass technologies and sub-systems, and for the supply, and administration of HPC systems themselves. According to multiple reports, investment in HPC can take a variety of forms: a) Buying HPC platforms and services, b) Developing technologies to feed into HPC systems, software and services, c) Using HPC to improve business processes, d) Using HPC to improve products and e) Supply of HPC support services, including compute cycles. HPC is able to generate huge rates of return (e.g. an IDC report<sup>2</sup>, which has a particular European context, argues that 'each euro invested in HPC on average returned €867 in increased revenue/income and €69 in profits'). The strategy adopted by the European Commission in 2012<sup>3</sup> highlights the need for intensified HPC technology provision in Europe and calls for an integrated and concerted effort by the entire European HPC industry. HPC is also one of the pillars of the Digital Single Market (DSM)<sup>4</sup> strategy adopted by the EC in 2015, which includes Big Data and Cloud and aims to build a basis for the long-term growth of the European 'digital' economy. This SRA serves as a tool to achieve the HPC-related objectives set in these strategies.

<sup>1</sup>www.ec.europa.eu/digital-agenda/en/high-performance-computingcontractual-public-private-partnership-hpc-cppp <sup>2</sup>IDC, 'High Performance Computing in the EU: Progress on the Implementation of the European HPC Strategy', 2015 (Commissioned by EC) <sup>3</sup>European Commission, 'High-Performance Computing: Europe's place in a Global Race', 15 Feb 2012

<sup>4</sup>European Commission, 'A Digital Single Market Strategy for Europe', 6 May 2015

## **CONTENTS**

| 1  | Fore                          | Foreword6                                                |    |  |

|----|-------------------------------|----------------------------------------------------------|----|--|

| 2  | Exe                           | Executive summary                                        |    |  |

| 3  | The European HPC Ecosystem    |                                                          | 8  |  |

|    | 3.1                           | SRA Update 2015                                          | 10 |  |

|    | 3.2                           | The Process                                              | 11 |  |

|    | 3.3                           | The elements of the Horizon 2020 HPC Roadmap             | 12 |  |

| 4  | Nev                           | <i>v</i> trends in HPC challenges, use and technology    | 14 |  |

| 5  | Technical Research Priorities |                                                          | 24 |  |

|    | 5.1                           | HPC System Architecture and Components                   | 26 |  |

|    | 5.2                           | System Software and Management                           | 29 |  |

|    | 5.3                           | Programming Environment                                  | 34 |  |

|    | 5.4                           | Energy and Resiliency                                    | 37 |  |

|    | 5.5                           | Balance Compute, I/O and Storage Performance             | 41 |  |

|    | 5.6                           | Big Data and HPC usage Models                            | 45 |  |

|    | 5.7                           | Mathematics and algorithms for extreme scale HPC systems | 47 |  |

| 6  | Res                           | earch milestones                                         | 52 |  |

|    | 6.1                           | HPC System Architecture and Components                   | 54 |  |

|    | 6.2                           | System Software and Management                           | 55 |  |

|    | 6.3                           | Programming Environment                                  | 56 |  |

|    | 6.4                           | Energy and Resiliency                                    | 58 |  |

|    | 6.5                           | Balance Compute, I/O and Storage Performance             | 59 |  |

|    | 6.6                           | Big Data and HPC usage Models                            | 60 |  |

|    | 6.7                           | Mathematics and algorithms for extreme scale HPC systems | 61 |  |

| 7  | End                           | -user and ISV requirements                               | 62 |  |

| 8  | Exti                          | eme-Scale Demonstrators                                  | 66 |  |

|    | 8.1                           | Approach                                                 | 68 |  |

|    | 8.2                           | Proposal of ETP4HPC for the EsD calls                    | 71 |  |

| 9  | Eco                           | system at large - stakeholders and initiatives           | 72 |  |

|    | 9.1                           | European Extreme Data and Computing Initiative           | 74 |  |

|    | 9.2                           | Eurolab4HPC                                              | 74 |  |

|    | 9.3                           | Centres of Excellence in Computing Applications          | 75 |  |

|    | 9.4                           | Big Data Value Association                               | 76 |  |

| 10 | Con                           | clusions and outlook                                     | 78 |  |

| 11 | Glo                           | ssary                                                    | 80 |  |

| 12 | Con                           | Contributions and Acknowledgements82                     |    |  |

# 1. FOREWORD

Since the first ETP4HPC Strategic Research Agenda (SRA) issued in 2013, High Performance Computing has gained even more recognition as a key technology for the future of science, industry and society. In addition to its role to provide an insight through large simulations in industrial and scientific fields, it is widely accepted that the digital economy will heavily benefit from HPC. The data economy, drawing on data provided by the Internet of Things and other sources, may improve the way we use resources and deliver services if HPC is used to analyse the data and make valuable judgement from it.

Developing this technology is a strategic move to accelerate the innovation and the deployment of the digitalised industry and data economy. Having a strong HPC ecosystem will enable the European players to benefit from the added value of the HPC value chain and will help to position HPC users at the forefront of their domains. Today, the HPC market is a fast growing one and represents a significant fraction of the IT infrastructures. HPC technology also has the potential to supply solutions to other IT fields, reinforcing its strategic position in a world that increasingly relies on IT. As one of the main trends of this domain, the interaction between users and technology is becoming crucial in order to take advantage of all the benefits of the advances made in HPC. Having strong expertise and skills in Europe is the key for maintaining a leading position in the use of HPC. We are confident that the contractual Public Private Partnership established between the European Commission and ETP4HPC will succeed in developing a world-class European HPC ecosystem.

This document is the first update of our Strategic Research Agenda. It aims to identify the research priorities for the European HPC technology community and reflects the point of view of the experts associated with ETP4HPC. Compared to the previous full issue, this SRA maintains the same overall direction but due largely to technology evolution, some of the milestones have changed and others have been revised.

To achieve this work, we have consulted with over 170 European HPC experts and I would like to thank them all for sharing their vision with us. We hope that this SRA Update will receive the same warm welcome as the first one and that it will help to shape leading edge research projects in the scope of the Horizon 2020 programme.

We (all) believe that this research program will be a key element in advancing Europe's global position in HPC and central to maximising the economic benefits from its exploitation.

ETP4HPC Chairman Jean-François Lavignon

# 2. EXECUTIVE SUMMARY

This document is an update to the European High-Performance Computing (HPC) Technology Strategic Research Agenda (SRA) issued in 2013 by ETP4HPC, the European HPC Technology Platform. ETP4HPC issues and maintains this SRA as a mechanism to provide contextual guidance to European Researchers and Businesses but also to guide EU priorities for research in the Horizon 2020 HPC programme. This SRA delineates a roadmap for the achievement of European exascale capabilities focusing on the following areas: HPC System Architecture and Components, Energy and Resiliency, Programming Environment, System Software and Management, Big Data and HPC Usage Models, Balance Compute, I/O and Storage Performance, Mathematics and algorithms for extreme scale HPC systems and Extreme-Scale Demonstrators. It is the work of experts associated with ETP4HPC and it also includes the input of industrial end-users, independent software vendors and other IT communities (e.g. Hipeac and BDVA). This SRA update will be followed by a full issue in 2017.

First, the strategic context of this roadmap is defined. These initial chapters help understand the elements of the European HPC ecosystem, the process of creating this roadmap and its role in the Horizon 2020 programme. Then, an update on the trends and challenges of HPC technology is presented.

The details of the areas of HPC technology targeted are in Chapter 5, which also includes references to the individual milestones listed in Chapter 6. Finally, Chapter 8 introduces the topic of Extreme-Scale Demonstrators which will serve to prove the context and relevance for the various technologies emerging; and build a European community in their supply-chain.

Whilst the research priorities presented in Chapter 5 and 6 apply to the FETHPC 2016-17 calls, the implementation of Extreme-Scale Demonstrators should take place in 2018-2019. ETP4HPC considers this concept as an important mid-term validation point of the research related to HPC technology within H2020, even though its implementation may require different funding mechanisms, or a new combination of the existing ones.

Whilst this report points heavily towards the H2020 HPC program for its delivery, the primary objective is to develop Europe's HPC ecosystem and maximise its exploitation. Accordingly, businesses and researchers who independently undertake these objectives to the benefit of Europe are to be applauded.

# THE EUROPEAN HPC ECOSYSTEM

The European HPC Ecosystem aims to develop world-class HPC technologies, platforms and applications, leading to exascale systems and their advanced use, thus creating jobs, new products and more efficient companies as well as enabling scientific discoveries. This will contribute to the economic competitiveness of the European economy as a whole and also to the well-being of the European citizen by equipping our scientists, economists, sociologists, agriculturalists, politicians and engineers to address the Grand Societal Challenges that the continent faces.

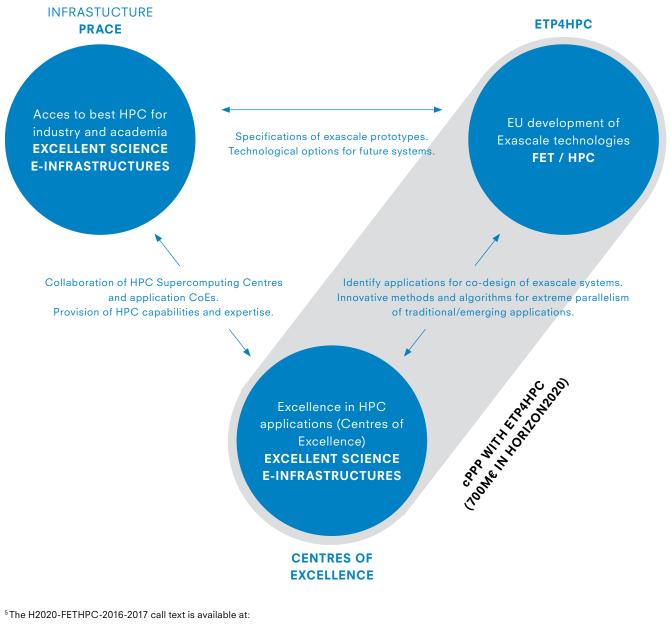

#### Figure 1

The three pillars of the European HPC Eco-system and the interactions between them. The HPC cPPP covers the areas of technology provision and application excellence. The FETHPC5 programme of the EC supports the development of European HPC technology while the EINFRA6 calls include the operation of the Centres of Excellence in Computing Applications. The separately funded EXDCI project provides mechanisms for the coordination of the entire strategy.

www.ec.europa.eu/research/participants/portal/desktop/en/opportunities/h2020/calls/h2020-fethpc-2016-2017.html#c,topics=callIdentifier/t/ H2020-FETHPC-2016-2017/1/1/1&callStatus/t/Forthcoming/1/1/0&callStatus/t/Open/1/1/0&callStatus/t/Closed/1/1/0&+identifier/desc <sup>6</sup>The EINFRA-21-2017 call text is available at:

www.ec.europa.eu/research/participants/portal/desktop/en/opportunities/h2020/topics/2122-einfra-21-2017.html

This European HPC Ecosystem (i.e. Technology Provision represented by ETP4HPC, Research Infrastructure represented by PRACE<sup>7</sup> and Application Expertise in the form of Centres of Excellence for Computing Applications) has entered a stage of rapid progress. The entire process is monitored by the contractual Public-Private Partnership (cPPP) for HPC, one of the eight European structures of this type.

The first FETHPC (Future and Emerging Technologies -HPC) technology research projects with a total combined value of almost  $\in 100M$  are due to be rolled out within the second half of 2015. These projects are based on the guidelines defined in the first ETP4HPC Strategic Research Agenda (SRA I, issued in 2013) of ETP4HPC. The first Centres of Excellence for Computing Applications<sup>89</sup> (CoEs) with a total investment value of  $\notin 40M$  have the start of their operation scheduled for the third quarter of 2015. These efforts form part of a  $\notin 700M$  investment package from the European Commission in this technology within the Horizon 2020 Research and Development Programme.

The EXDCI (European Extreme Data and Computing Initiative) coordination and support action (CSA) project is led by PRACE, in close partnership with ETP4PC. It embodies the expertise and experience of EESI<sup>10</sup> and a portfolio of independent experts aims to specifically stimulate and coordinate the European HPC strategy. It is scheduled to operate from September 2015 for two and a half years. Its mission is to monitor, coordinate and support this strategy of the European HPC Ecosystem, providing tools for: technology 'roadmapping', analysing academic needs, international collaboration and education and training across the three pillars of European HPC (Infrastructure, Technology and Applications).

A separate coordination project (Eurolab-4-HPC<sup>11</sup>, see also Chapter 9) will operate in parallel with EXDCI and will focus on Excellence in High-Performance Computing Systems and longer-term research in computing architectures and HPC beyond 2020.

## 3.1 SRA UPDATE 2015

This Strategic Research Agenda (SRA) Update is a part of the continuous process of maintaining the European HPC Technology Roadmap by ETP4HPC. The SRA document is an important tool for establishing the European HPC Technology Roadmap and guiding the subsequent H2020 funding programmes. For this reason, it needs to be continually revised. ETP4HPC plans to carry out a full SRA revision every four years and interspace them with mid-term updates.

The first issue of the SRA was written in 2013 (SRA 1) and its recommendations form the basis of the first FETHPC (Future and Emerging Technologies HPC) research call within the Horizon 2020 programme. This is the first midterm update, and should be read in conjunction with the 2013 release. The SRA is a living document and will be used to define the subsequent research calls. ETP4HPC has embarked on the process of issuing this document (i.e. SRA 2) as an update to SRA 1, reflecting the changes that we know have occurred, i.e.

• The first round of FETHPC calls (FETHPC-I-20I4) addressed a number of milestones identified in SRA I. The projects resulting from that call are now in progress and they are expected to produce solutions that future projects might choose to build on.

$\cdot$  The HPC Ecosystem has witnessed technology developments within and beyond Europe that need to be mirrored in the roadmap. A separate chapter is dedicated to those changes, which have an effect on the original milestones defined in SRA I.

$\cdot$  SRA I was designed in the early stages of the operation of ETP4HPC. The membership base of the organisation has multiplied since and this update allows new members to include their point of view in the roadmap.

#### <sup>7</sup>www.prace-ri.eu

<sup>8</sup>A summary of the Centres of Excellence in Computing Applications is available at: www.ec.europa.eu/programmes/horizon2020/en/news/ eight-new-centres-excellence-computing-applications

<sup>9</sup>The EINFRA-5-2015 call text including the Centres of Excellence in

Computing Applications is available at: www.ec.europa.eu/research/ participants/portal/desktop/en/opportunities/h2020/topics/329einfra-5-2015.html <sup>10</sup>www.eesi-project.eu

<sup>11</sup> www.cordis.europa.eu/project/rcn/197540\_en.html

• In a similar vein, the European HPC Ecosystem has evolved significantly since 2013. Measures have been put in place to monitor and coordinate its strategy. The contractual Public-Private Partnership between the EC and ETP4HPC aims to ensure the commitment of all stakeholders in the development of the Ecosystem. The EXDCI project (see Chapter 9.1) synchronises the efforts of the Ecosystem order to achieve the agreed objectives. This SRA update reflects this maturity through the increased involvement of all stakeholders (with an emphasis on industrial HPC end-users).

Whilst constituting a ~90 page document, this SRA 2 is still an update of the first 2013 SRA and mainly provides refreshed technical content in Chapter 5. As scheduled, this update will be followed by a full issue of the SRA in 2017 (SRA 3) and a further update in 2019. We look forward to constructive contributions to those from a wider community in due course.

## 3.2 THE PROCESS

The process of preparing this update began in January 2015. First, a global analysis of the trends in HPC challenges, use and technology was performed. This analysis is presented in Chapter 4. From this work emerged eight areas of the European HPC Technology Roadmap:

- · HPC System Architecture and Components

- · System Software and Management

- · Programming Environment

- · Energy and Resiliency

- · Balance Compute, I/O and Storage Performance

- · Big Data and HPC Usage Models

- $\cdot$  Mathematics and algorithms for extreme scale HPC systems

- · Extreme-Scale Demonstrators

All ETP4HPC members were invited to participate in technical working groups, mirroring the categories above. The working groups were led by selected members of ETP4HPC, who produced the content of Chapters 4 to 6. The topics of "Mathematics and Algorithms for extreme scale HPC systems" and "Extreme-Scale Demonstrators" are introduced by this update as they did not appear in SRA 1.

In June 2015, two workshops involving external experts were organised to verify the validity of the document's assumptions taking into account the requirements of the market. First, a workshop involving industrial HPC end-users was held to obtain their feedback in relation to their system requirements. Then, a similar event with the involvement of Independent Software Vendors (ISVs) took place (see Chapter 7).

After two successful project phases and a final conference in May 2015 in Dublin, EESI/EESI2 coordination and support actions published final recommendations on strategic European actions with a particular focus on software key issues improvement<sup>12</sup>. EESI2 made a selection of key recommendations in the areas of Tools & Programming Models, Ultra-Scalable Algorithms and Data Centric Approaches. These recommendations are complementary to and consistent with the ETP4HPC ones. A workshop between EESI2 and ETP4HPC was held in Dublin and different EESI experts participated in the SRA workgroups.

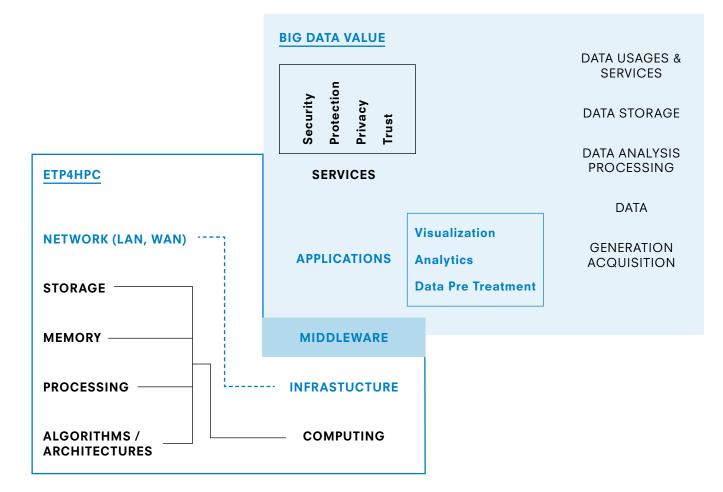

The Big Data community has been consulted during the preparation of this SRA. A workshop was held in July 2015 to discuss the converging areas of technology addressing the needs of both communities. This input has been used to propose some of the milestones of the R&D roadmap.

<sup>12</sup> www.eesi-project.eu

an interim deliverable is at: www.www.eesi-project.eu/wp-content/ uploads/2015/05/EESI2-ALL-RECOM-July2014.pdf

### 3.3

## THE ELEMENTS OF THE HORIZON 2020 HPC ROADMAP

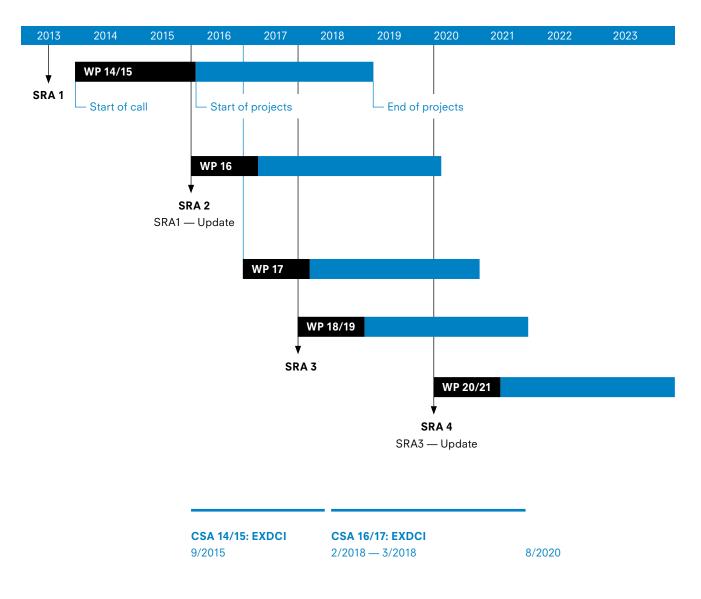

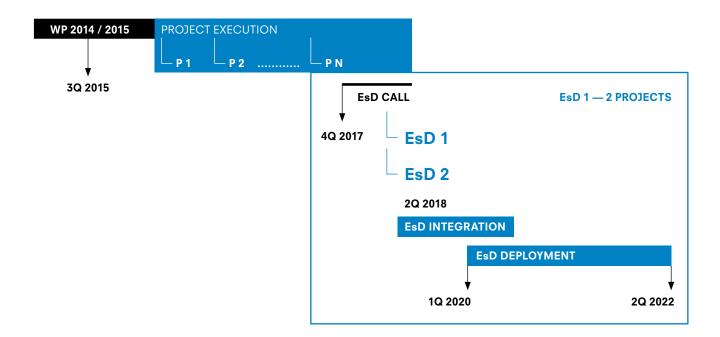

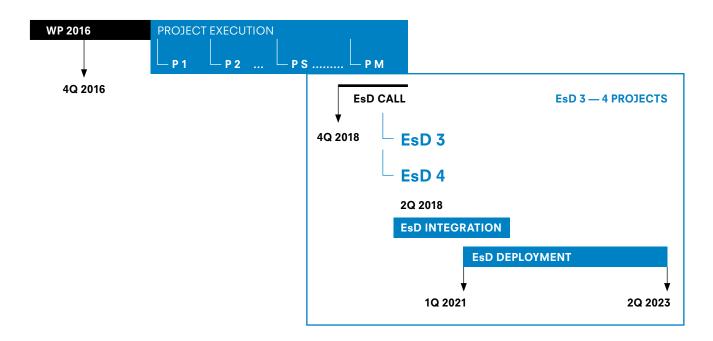

Over the last two years the Horizon 2020 roadmap for HPC related work programmes and other actions have evolved significantly. ETP4HPC's current view of the timing of this Programme's various components is outlined in Figure 2.

$\cdot$  The Work Programme 2014/2015 (WP14/15) has resulted in nineteen accepted projects being launched at the time of writing this document and beginning their operation in Q4 2015.

• The call for WP2016 will open in the Q4 2015 while the call for 2017 will open a year later.

• The two following Work Programmes are shown tentatively and at this moment they should be considered as 'under evaluation'.

• The Coordination & Support Action (CSA) called "EXDCI" (see Chapter 9.1) started in September 2015. ETP4HPC has proposed to continue this type of support throughout the entire Horizon 2020 (CSA 16/17).

• As mentioned in the SRA 1, ETP4HPC strongly recommends building HPC System prototypes, in the pre-exascale timeframe (2018/19), as proof-points for the effectiveness of the Work Programmes 2014/15 and 2016/2017. This concept called "Extreme-Scale Demonstrators" is outlined in Chapter 8.

• ETP4HPC is committed to renewing the SRA document for each new Work Programme call to ensure that the parties interested in submitting a proposal have access to an up-to-date roadmap including the relevant research topics and the supporting actions. This SRA 2 (an update of SRA 1) is therefore planned to be released by 20th October 2015.

## HPC — HORIZON 2020 ROADMAP

#### Figure 2

ETP4HPC's view of the Horizon 2020 HPC roadmap: the timelines of the relevant Work Programmes (WPs).

## NEW TRENDS IN HPC CHALLENGES, USE AND TECHNOLOGY

This chapter provides a high-level view on the latest trends identified in the various fields of HPC technology – from chip to system – and new ways of using HPC infrastructure.

The "Multi-dimensional HPC Vision" introduced in Chapter 4 of the SRA I is still valid and has proven to be useful in dealing with the multiple facets of HPC technology.

There is a demand for R&D and innovation in both extreme performance systems and mid-range HPC systems. Almost all scientific domains and some industrial users want to achieve extreme-scale performance systems as soon as possible. At the same time, there is a need, particularly expressed by industrial users and ISVs, for more flexible, easier-to-use, more productive and cost-effective HPC systems delivering mid-range performance.

The ETP4HPC HPC technology providers are also convinced that to build a sustainable ecosystem, their R&D investments should target not only the exascale objective. This market will be too narrow to yield a sufficient return on investment and support sustainable technology development, and that such a strategy would weaken the European players. On the contrary, an approach that aims at developing technologies capable of serving both the extreme-scale requirements and mid-market needs can be successful in strengthening Europe's position. As a consequence, the SRA has two dimensions: one targeting the R&D aiming at developing the new technologies able to offer more competitive and innovative HPC systems for a broad HPC market, and another to enhance these technologies with the right characteristics to address the extreme-scale requirements.

The third element is the trend of developing new HPC applications. Besides traditional HPC workloads, more and more Big Data applications will need to be addressed with HPC solutions. There is also a request from some domains to use HPC systems for the control of complex systems, such as smart grids. The Cloud delivery model is yet another trend that will impact the features of future HPC solutions. Accordingly, the SRA has a dimension to address all these new usages.

There is also a major concern that some of the stakeholders of HPC development could be limited by some barriers, namely shortage of skills, insufficient availability of services to fill the gap between potential user demands and HPC solution offerings, usability of solutions or flexibility and vitality of the ecosystem. The fourth dimension identified in this SRA reflects these concerns.

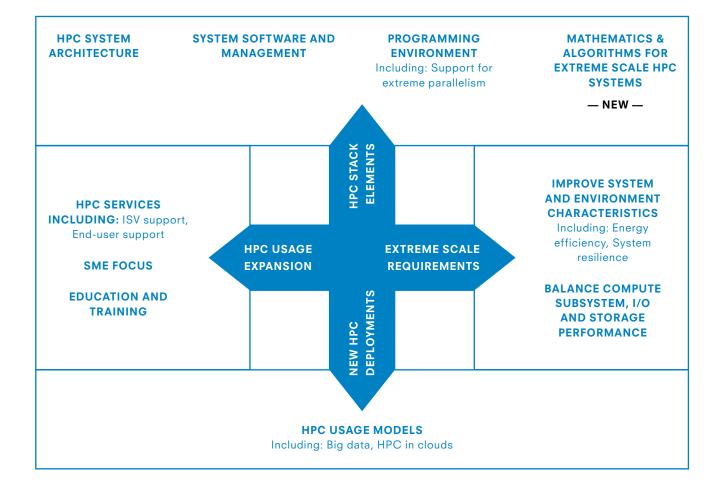

Some changes need to be introduced to these four dimensions to take into account some of the evolutions of the last two years. Figure 3 provides an updated version of our four-dimensional view of HPC technology development:

#### Figure 3

The new four-dimensional model of European HPC technology development based on its first version as defined in SRA 1 (2013)

The following additions and amendments seemed necessary:

• A new research field was added to the dimension "HPC Stack Elements" called "Mathematics and algorithms for extreme scale HPC systems". Mathematical methods and algorithms play an increasingly important role for both, providing HPC technologies as well as using HPC technologies efficiently. By adding this new dimension, ETP4HPC acknowledges the key role of mathematical methods and algorithms for future development of HPC architectures and technologies. It will engage in this broad and active area of research, taking into particular account the impact on the commercial stakeholders. One example is the methods for scalable data analytics, an area which is predominantly driven by commercial operators and where huge progress in algorithms is required to make them scalable.

• The two topics "usability" and "affordability", although still essential and among the top priorities of academic and industrial end-users need to be dealt with in a very integrative way on the HPC architecture level. They both are basic drivers for new HPC stack technology updates, especially in the areas of system software, programming environments as well as power efficiency. The seven technology domains in Chapter 5 spell out new research priorities taking demands for usability and affordability into account. Thus, these two aspects will not be handled separately any more.

There are three topics, not or only marginally addressed in the SRA 1, receiving increasing attention: "Security in HPC infrastructures", "resource virtualisation" and "HPC in clouds":

• Keeping computer systems, and the information stored/ processed on them secure by preventing unauthorised access, use or modification is clearly a very important task across all fields of computing. Hence, a great variety of R&D projects on architectures, systems and measures that enhance system and data security, are being carried out by many academic and commercial players, and results are increasingly put into operational use. The prevalent HPC usage Model has profited from advances in authentication and authorisation of users, in securing high-speed data communication, and in access control for datasets. Since all three topics are shared with most other fields of computing, it does seem reasonable to continue to leverage advances in these fields. No specific and unique requirements from HPC were identified here; and, of course, it will be important for HPC R&D projects to be aware of said security provisions and accommodate them across the full stack (from hardware to services). Since this is a horizontal and mainly implementation concern, we do not propose specific security priorities, objectives or milestones in this document. Emerging HPC use cases (Cloud, Big Data) do add security concerns not present in the classical HPC environment. The attack surface grows through the use of services, increased commercial value at stake and the handling of valuable and personal or commercially relevant data. Therefore, R&D targeting these use cases needs to accommodate a high-level of data protection against outside as well as inside attacks; existing and continually improved methods for end-to-end encryption, dynamic enforcement of fine-grained access privileges, and detailed data access logs can be leveraged here. Again, we do not propose specific security priorities, objectives or milestones here; requirements to provide support for security layers is mentioned where appropriate.

• **CPU**, **device and network virtualisation** has enabled significant efficiency and reliability in Enterprise computing. Its uptake in HPC has been extremely limited, mainly due to concerns about performance and vendor lock-in. With advances in network virtualisation, an example of a compelling use case is emerging: being able to move all or parts of a "virtual HPC Cluster" to different HW transparently to the workloads in case of impending failures, or to accommodate partial system maintenance which would substantially increase availability of a system, and thus, address resiliency concerns. This will require a careful combination of CPU virtualisation (or containers) and network virtualisation, and is discussed in Chapters 5.2 and 5.5.

• Leveraging Cloud mechanisms to provide universal and simple access to HPC systems and services is by no means a new idea. Commercial players (e.g. Amazon) have had good initial success in offering Web-Service based access to HPC-class resources in certain niches, e.g. genome analysis workflows. For most other usage areas of HPC, the uptake of Cloud is still in a very early phase. The "Fortissimo" FP7 project, for instance, has created an HPC marketplace, which makes HW and SW resources at several HPC centres available for small and medium-sized enterprises in the manufacturing area. About 30 targeted experiments have shown the value of such a model to the end users, and have resulted in prototypes for HPC services.

The following paragraphs provide an overview of the current status and the latest trends perceived in the seven SRA technical domains:

- · HPC System Architecture and Components

- · System Software and Management

- · Programming Environment

- · Energy and Resiliency

- · Balance Compute, I/O and Storage Performance

- · Big Data and HPC usage Models

- · Mathematics and algorithms for extreme scale HPC systems

This overview allows the Reader to put the research priorities listed and explained in detail in Chapter 5, in the perspective of the overall picture presented here.

To keep up with the ever demanding HPC user needs, the performance of HPC systems at all scales must grow faster than the regular progress of computing technology. A disruptive approach is needed and it requires changing **the ar-chitecture of HPC systems**, from chip level to complete systems by integrating new technologies for processing units, memory, storage, networking, etc.

Most significantly, the recent use of HPC accelerators (e.g. GPUs, Many-core CPUs) has resulted in a significant performance boost for some applications. To enlarge the application scope of these HPC accelerators they must be better integrated in the architecture of the HPC nodes or at the system level. To deliver performance, these HPC processing units must access data with a much higher bandwidth than is available with today's DRAM memory technology. This is possible with the introduction of high-bandwidth memory in addition to or in lieu of DRAM. To overcome the limited capacity of these fast memories and to fully leverage their potential, a complete re-engineering and re-architecting of HPC applications might be required.

New non-volatile memory technologies (NVRAM, also referred to as "SCM-storage class memory") appear to be on the near horizon. It is expected that they will offer a much larger capacity than current DRAM, a good fraction of DRAM bandwidth and similar endurance. This opens interesting opportunities for the design of HPC systems. Long-term, the new NVRAM could replace DRAM altogether in compute nodes and become the base for ultrafast storage at the same time. These are technologies which would greatly improve the ability to check-point/restart runs which have failed.

HPC systems are highly parallel. The many thousands of nodes available in an HPC system must be tightly coupled by an efficient network which also integrates storage. The HPC system network must scale with the number and performance of compute nodes and storage devices, requiring more bandwidth but also cutting latencies through better integration. The HPC network should also simplify the application development providing a simple access to the whole system resources. As mentioned above, virtualisation is making its way into the HCP system design and is essential for a more flexible usage of HPC systems; it will also increase system resiliency through Check-Point/Restart and help to deliver improved fault tolerance and robustness, e.g. by allowing defective nodes to be excluded. Network Virtualisation will be an important part of this. The improved flexibility will also facilitate access to HPC as a cloud resource, enabling new business and usage models through agile, on-demand infrastructures.

Finally, new High Performance Data Analysis (HPDA) applications are emerging alongside with HPC. There seems to be quite of lot of common requirements between these two domains. The new HPDA field could profit significantly from using HPC technology. Conversely, HPC architecture should take into account HPDA specifics and requirements as they emerge.

During the creation of SRA 1 in 2013, important stages of the evolution of **system software and management** building blocks were clearly identified. Unfortunately, it seems that some expected research goals are delayed.

The operating system currently has to take into account new intra-node architectures with many cores, mesh system bus and a heterogeneous memory model. New NUMA-type topologies for memory, I/O, and sockets are proposed. The impact of this node architecture and the intensive use of Multi-threaded programming models increase the need for tools, instrumentation and actuators to solve the scalability and concurrency issues introduced by more complex node architectures. This is seen as a critical research topic.

Sharing of computing resources between some HPC and Big Data domains is increasingly considered. The Big Data "revolution" has put more emphasis on new system software requirements, such as virtualisation support, data centric management, and close-to real-time capabilities. Of course, supercomputer-class storage and I/O subsystems, interconnects and processing capabilities can solve many issues of Big Data, yet progress in the system software field is required here.

Virtualisation, data security at hardware and system level becomes a critical challenge for exascale infrastructure which could address new Big Data use cases. High Performance Data Analytics (HPDA) will explore the convergence of those two domains. System software will need enhancements to support it.

In HPC, Interconnect research development has been mainly driven by performance and scalability. Network Virtualisation and QOS are still open issues for HPC interconnect fabrics. It could be an interesting challenge to find the balance between performance and virtualisation capabilities.

New interconnect hardware based operation and new memory (NVRAM) capabilities combined with large scale simulation have a strong impact on "in-situ" processing requirements. In-situ processing use cases are mainly concentrated in visualisation, snapshotting or real-time domains.

High bandwidth links offer new capabilities for interactions in heterogeneous nodes enabling new data transfer capabilities and shared memory access. At the system and network level, it will require specific investments in tools and low level APIs to offer access to counters and registers in order to understand global data move issues (congestion, locking, routing trouble shooting, etc.).

The evolution of Cluster Management tools to introduce onthe-fly data analysis and post-mortem data mining started in 2015 but is still incomplete. Event-driven health-checking and introspection is vital for stable operation. Modularity and heterogeneity of the system configuration require the development of an advanced integration model.

Resource management and job scheduling are a critical piece of software for a Big Data framework as well as for HPC supercomputers. Several improvements will be necessary to reach - with a good level of scalability - the multi-criteria objective such as highest allocation flexibility, tightly coupled with application- and software environment deployment. Alternatively, new allocation criteria could be taken into account (e.g. network topologies, interconnect bandwidth, I/O associated workflow, CPU architectures and new memory hierarchy architectures). Significant software evolution will be required in resource and task scheduling to support the run-time environment of new systems.

In the domain of **Programming Environment**, to allow portable performance of applications at extreme scales, we require the development of more productive programming models and environments (including support for domain-specific languages), the easier combination of different programming

models, programming models supported throughout the developer tool chain, and the coherent adaptation of applications in co-design with the lower-level environment.

A most promising development is the inclusion of increased intelligence throughout the programming workflow, from the top-level application down to low-level system software. Important examples of how intelligence in the programming environment can facilitate enhanced performance and enhanced productivity in application software development are:

• Application-level abstractions can be used to allow the run-time system (where run-time system is understood here and in the corresponding section of Chapter 5 to encompass programming model support, communication middleware, realisations of APIs and application support libraries) to optimise data layout and data movement, improving performance and energy use and avoiding complex, platform-dependent application software adaptation.

• Hint frameworks within the programming environment enable the application user to make assertions about potential concurrency or locality.

• Application-level abstractions and hint frameworks may be used by the run-time system to enable dynamic resource use (malleability and load balancing, discussed in detail in Chapter 5.3).

• Using techniques from data analytics, performance tools can integrate increased intelligence to provide insight into the behaviour of full production software at scale in order to improve scalability, performance or energy efficiency.

Enhancing the productivity of application software developers for large-and extreme-scale systems is central to a number of trends: domain specific languages (DSLs) should allow the application developer to concentrate on domain-specific problem-solving, whilst allowing lower-level software components to generate optimised code across different architectures; generalisation and extension of past progress in auto- and self-tuning parallel libraries can lead to meta-programming environments and corresponding meta-scheduling support (run-time) systems; interoperability and composability of programming models improves comprehension and provides flexibility for the software developer and should ensure, at the same time, that the system software efficiently exploits the physical resources. There is a common growth in the deployment of heterogeneous, parallel computing architectures (including, but not limited to, FPGAs, customised processors system-on-chips (SoCs) in embedded and HPC systems, which can benefit the developments towards exascale. There is a significant potential for harnessing developments in the programming environment to facilitate software portability and to benefit from the enlarged developer and user communities.

Finally, while resilience is a topic addressed as a separate topic within the SRA, it is ensuring the resilience of applications executing at scale impacts directly on all sub-themes within the Programming Environment area. Indeed, it could be considered as a key-topic orthogonal to those described above.

In a computer, **electrical energy** is converted to heat by the function of the switching gates and leakage current, producing human interpreted computational results as a side effect. "Energy efficiency" of this process has two meanings: efficient extraction of the emerging heat and reduction of the electrical energy spent while obtaining the computational results by increasing the efficiency of data manipulation and computation itself (Flops/watt).

The focus in the reduction of the spent electrical energy is twofold. Firstly, reduction of losses. Being addressed today by techniques such as the Point-of-Load (PoL) voltage conversion utilising solid-state switched voltage conversion devices. Losses can be reduced by tenfold when combined with adequate cooling for heat extraction. Secondly, reduction of data movement results in huge energy savings, and this is achieved by architectural changes in computers and better organisation of the computational process.

For the computational process – it is a challenge and necessary research topic to render energy spent in computer proportional to the perceived computational advance. The notion of computational advance as a function of energy spent needs better quantification before methods are implemented to make the two proportional.

Another possible energy reduction measure is the acceptance of lower precision result in HPC calculations, trading accuracy for energy usage. Whether this approach can be used will depend on the specific application and algorithm, making this a challenge for energy efficient scientific libraries. Modern HPC system designs come with increased levels of memory hierarchy and a drastically increased number of hardware processing units running in parallel with the goal to reach exascale performance. With a larger number of processing units, the hardware failure rates increase and **resiliency research** explores ways to minimise impact of failing components on computation. The organisation of a checkpoint is one way to restart the computation after a failure, as well as a way to expand or contract computation on a varying number of processing elements and manage it based on the partial outcome. The challenge is to find a balance between hardware support and software transparency to adopt this technology in a broader manner.

Resiliency is gained if failures can be predicted; the challenge being to determine which data must be collected to make such predictions. Specific failure statistics must be gathered for this research to advance.

The increased efficiency in heat extraction is addressed by replacing air through liquid with higher heat capacity (e.g. water). This presents a tremendous opportunity for computer cooling infrastructures. There are many ways to eliminate air from its current heat-carrying role with industry moving towards the best price/performance technology. The industrial challenge here is the completeness of heat capture into water; a mixture of air-cooled and water-cooled technology diminishes advantages of both. Data centre efficiency is gained when water can be cooled by natural conduction in atmosphere (free hot water cooling) instead of phase-change cooling, requiring extra energy. Water handling infrastructure for "free hot water cooling" is well established, but its usage in computer centres is a novelty that needs a larger number of use cases to support wider adoption. A special research topic is the re-using of the heat instead of dissipating it into the atmosphere. This may be addressed by co-location computer centres with consumers of such heat sources, but more use cases are needed to quantify the perceived advantages.

**Storage and I/O** performance improvements typically lag behind compute performance especially with the arrival of increasing heterogeneity in the compute subsystem (much greater now than in 2013 SRA 1), with the proliferation of multi-core and many core architectures and the arrival of new technologies in the HPC ecosystem such as GPGPUs. Complexity and parallelism in the compute subsystem has increased by about an order of magnitude in the last few years. However, storage subsystem has still not (in the time leading to this SRA update) kept up with the needs of applications that have started to exploit the benefits of such heterogeneous and highly parallel compute architectures. There have been research initiatives, but industry roadmaps for storage and I/O are still largely making incremental improvements to incumbent solutions - these will soon start to reach fundamental limitations as they were architected for a different era when compute subsystems and applications were very different. We are starting to see many activities in object storage technologies that offer a flat namespace<sup>13</sup>, and aim to address some of the limitations of parallel file systems. Some of the open source objects storage technologies are now starting to gain adoption in HPC. However, even object storage technologies today are far too simplistic in their approach, and are mainly architected for cloud archival workloads, and not for highly performance critical and highly parallel HPC workloads. We anticipate a major architectural revamp of object storage technologies in response to increasing heterogeneity and parallelism.

Storage sub-systems (perhaps driven by advanced object store software) will need to continue to show balanced I/O performance with respect to compute capability and the increasing lag between compute and I/O has to be immediately addressed. Otherwise, we will risk having very powerful compute subsystems, which have to heavily compromise on I/O, workload that is going to be a big detriment for big science and innovation, especially, with Big Data entering the HPC realm.

The use of new solid-state non-volatile devices, starting today with the early use of FLASH technology in HPC deployments, is expected to include other technologies with performance closer to RAM and with longevity suitable for these environments. Exactly when such technologies will reach a maturity, scale and cost suitable for deployment in the massive scale of HPC is still unclear but it is believed to be a necessary component of any exascale solution. Smaller capacity, higher cost but highly performing devices must co-exist in a system with a range of other storage devices (solid state, disk or tape based) and a significant challenge will be created in the management of data across such systems. There is a need for the storage subsystem to become more "intelligent" in their ability to do computations, and hence, achieve better task sharing between compute and I/O. The portion of energy budget for storage and I/O, which are continuing to creep up because of Big Data I/O, has to be kept under check. There is also a need to maintain or improve systems resiliency with continuously failing I/O and storage components. Some of these storage components may be an entirely new class of NVRAM based storage technologies, residing in multi-layered I/O structures along with existing storage device technologies. The reliability behaviour of these new devices is not very well understood, especially at scale.

Dealing with extreme data is a situation that manifests itself with fast increasing frequency of HPC systems. The root causes stem from two main categories:

Traditional HPC simulations (e.g. fluid dynamics, computational chemistry and physics, cosmology among others) have been benefitting from the tremendous increases in computational capacity of HPC systems and are now using models of unprecedented realism and accuracy. These models represent the real world using trillions of discrete degrees of freedom, which require huge RAM and scale out systems. On the other hand, researchers need to apply advanced and highly complex analytics and processing (including visualisation) on this data, which simply means that off-loading this data to remote platforms is simply not an option. Thus, data analytics needs to take place in-situ, and perhaps in synchrony with tightly coupled synergistic computing platforms (e.g. visualisation engines).

On the other hand, new applications arise as potential HPC clients. Big Data applications, in which data is not generated from some sort of model but rather is collected, accumulated or even streamed, and comes with computational complexity that already sets the computational needs to the petascale or even to the exascale region, even after local pre-processing. Big Data systems, that have been primarily developed for scale out to distributed, non-reliable, resources, are simply too coarse in efficiency and cost effectively to cope with such computational complexity. Thus, HPC solutions, with lots of memory and very fast networks start to appear very appealing and are the next natural step for Big Data users. Indeed, Big Data systems have already started to be influenced from HPC architectures and practices (e.g. multi-threading, parallelism, memory modelling etc.). On the other hand, it is also clear that data will be

<sup>&</sup>lt;sup>13</sup>For example: Ceph Website www.ceph.com, Accessed November 2014

highly distributed as it originates from distributed sources. Thus, synergy of Big Data systems and tightly coupled HPC systems is foreseen in forming a larger, hybrid, computing resource that combines local and global processing to serve the needs of the new kind of Big Data applications.

Advances in mathematical methods and algorithms will be essential in order to produce robust applications that can leverage future high-performance exascale architectures and to reach the goal of improving energy efficiency by two orders of magnitude. Significant efforts in this area are required to allow applications to become even more parallel, scalable and robust, and to optimise for data locality on architectures with deepening and heterogeneous memory hierarchies. New challenges arising from emerging application areas that require both, high-performance computing resources, as well as the ability to manage and process extreme amounts of data should be addressed. The impacts of research on mathematical methods will not be confined to applications, but will equally influence the design of future exascale system software like compilers, communication libraries and programming environments. Notably, the area of optimisation and scheduling will benefit from new mathematically motivated approaches. The interaction with exascale programming environments will be important, as those environments will provide the platform through which new mathematical methods and algorithms will be realised in software applications.

Mathematical methods and algorithms is a new area addressed within the ETP4HPC's SRA. The agenda will focus on research required to achieve extreme scale performance, and in particular, take into account the impact on the commercial stakeholders that include:

• Users of HPC resources that benefit from the development of new methods for solving numerical and extreme data challenges, in particular, in the area of industrial and engineering applications as well as emerging Big Data applications;

• HPC hardware system vendors who look for algorithms that enable most efficient exploitation of their solutions;

• Software solution and service providers (e.g. ISVs), for which new and robust mathematical methods and algorithms are crucial in providing more competitive software solutions and to enable SaaS services, e.g. based on HPC in Cloud concepts.

This new area of the ETP4HPC SRA and other efforts within the European HPC ecosystem, in particular, the work of the "European eXtreme Data and Computing Initiative" (EXDCI), are interdependent. This makes the cross-coordination of activities crucial. Furthermore, the emerging Centres of Excellence will aggregate significant expertise in mathematical methods and algorithms and will be a key player in driving further research in this field.

a k of uses of High-End Technolog. Broductionity + ficiency (\$, energy. and the second

## TECHNICAL RESEARCH PRIORITIES

This chapter contains the essence of the updated research roadmap. Compared with the first SRA, it provides substantially more topics spanning a broader area of technical challenges to be mastered. It also provides more insight into the specific research requirements. The research topics are linked to "Research Milestones" listed in Chapter 6. Please also refer to Chapter 4 for a general introduction into and an overview of the required work outlined in this chapter.

The overall goal of the research proposed is defined by the following five objectives:

• **Exascale and extreme scale:** to substantially improve the ability for technology providers in Europe to deliver exascale-capable HPC technologies across the entire HPC stack by 2023. As already mentioned in Chapter 4, besides being in a position to provide exascale compute infrastructure to top-end HPC users in Europe, the HPC industry should be in a position to master the entire spectrum from low to high-end scale sizes, adopting and re-using the technology advancements from the extreme (exa)-scale at the high-end.

• **Ease-of-use:** there are two dimensions of ease-of-use becoming most relevant: being able to "handle", manage and efficiently use extreme scale HPC infrastructures on one side and facilitate the generation and porting of applications on much higher scale compute structures, heterogeneous compute nodes and multi-layer memory subsystems on the other.

• Efficiency: Energy efficiency is a key element here, reducing the Total Cost of Ownership (TCO) and is certainly another important goal, especially in the light of extreme scale HPC infrastructures as well as enabling a higher utilisation of all resources.

• Enabling extreme data & extreme computing: contribute to the development of a "data-centric" focus across the entire stack and facilitate HPC technology, becoming the underpinning compute infrastructure of choice of high demand Extreme data applications.

• **Broadening of HPC use:** A new term, "democratisation of HPC", has been coined, referring to HPC becoming available by a much broader set of industrial users, in particular SMEs and research organisations. Affordability, down-ward scalability, ease-of-access, and effective programming environments play a key role here.

The following Sections (5.1 - 5.7) describe the areas of European HPC technology in detail. Chapter 6 lists the milestones to be accomplished. These milestones are referred to in the text of Chapter 5 using the following convention, e.g.: [M - AREA CODE – NUMBER].

## 5.1 HPC SYSTEM ARCHITECTURE AND COMPONENTS

To meet the ever demanding requirements for performance, HPC systems must keep evolving. Simply following technology evolution is not enough as improvements are too slow in meeting targets. Disruptive approaches are needed and the use of new technologies is required. In particular, HPC systems will feature much faster nodes using HPC processing units, faster/larger memory and storage devices, and also, better interconnect. Power efficiency is the main roadblock towards exascale, so all such performance gains should not increase power needs.

#### 5.1.1 Compute nodes — HPC processing units

Recently HPC systems have been deployed using HPC accelerators such as GPUs or Many-cores accelerators. These units are highly parallel and use hundreds/thousands of threads to deliver the performance. These cores run slower than those in generic CPUs, and thus, will not be usable for single thread performance sensitive applications. To improve their efficiency, these HPC processing units must be better integrated into the system architecture than they are as accelerators. The current versions use a generic PCIe interface; it will be improved at the hardware level with coherent interface or as a standalone processor. Even with these improvements, the architecture might be too complex for large HPC applications. Programming Environment should provide a standard interface to hide this complexity; at the hardware level the appropriate features should be available. The simple flat parallelism model with a compute thread corresponding to an MPI task will not scale. A hybrid approach MPI+X (where X could be OpenMP, OpenAcc) or PGAS +X should be enabled. [M-ARCH-1]

#### 5.1.2 Data Access — HW components

Although CPUs and HPC accelerators have improved drastically, the peak performance of the compute nodes and the delivered performance at the applications level have been lagging. The growing gap between theoretical and delivered performance is directly connected to slow improvement in memory speeds; this is often referred to as the "memory wall". To overcome this limitation, fast memory (GDDR, HMC, HBM ... ) is been embedded with HPC accelerators. These fast memories have a smaller capacity than DRAM memory, and thus, are adding an extra level in the memory hierarchy. To add complexity, these fast memories must be addressed explicitly by the programmer and/or run-time systems, if not, just used as a functionally transparent caching layer that may be of little use. In general, delivering improvements in bandwidth and latency can have major impacts on code efficiency<sup>14</sup>. Thus, the challenge is to find the right balance between future memory bandwidth, latency, size, power consumption and cost. [M-ARCH-2]

Upcoming Non-Volatile Memory (NVRAM) technologies are opening new opportunities for HPC systems. New NVRAM will feature much larger byte-addressable capacities as DRAM: hundreds of GBs vs tens of GBs. Their performance (read or write BW) will be much better than current FLASH based NVRAM, approaching DRAM levels. Furthermore, their endurance should be comparable with DRAM at least in combination with some hidden wear-levelling technology. They could be used in HPC systems, both as main memory and ultra-fast IO, and would completely change the system programming model which distinguishes memory and storage (files), see also Multi-tier storage in Balance Compute, I/O and Storage. [M-ARCH-3]

14 www.memsys.io/wp-content/uploads/2015/09/p31-radulovic.pdf

#### 5.1.3 HPC Systems Interconnect

HPC systems are composed of a large number of nodes, from 100 for a departmental system to 10,000s for the Top10 systems. The application performance relies on parallelism and depends directly on the efficiency of the interconnect unifying the compute nodes into a single system. The HPC system interconnection network must scale together with the compute nodes and the storage performance. The HPC networks bandwidth is planned to grow from a standard 100 Gb/s in 2016, to 200, then 400 Gb/s in the following years.

With such transmission rates, the possible range for electrical connections will shorten and optical links will become prominent. Underlying network technology improvements are expected in areas such as silicon photonics and photonic switching, which should enable scale performance whilst keeping consumption under control. [M-ARCH-4]

Independent of the BW increase just mentioned, Network efficiency is another topic of interest. Reducing communication latencies will require integrating Network components with compute and storage resources. Other improvements will come from system fabric optimisation, with new topologies, dynamic routing and resource scheduling, in order to avoid network congestion. [M-ARCH-5]

Direct access to the whole system memory should enable new ways to program parallel applications. In particular, the evolution of today's PGAS (Partitioned Global Address Space) programming languages will simplify the implementations of HPC applications. [M-ARCH-6]

#### 5.1.4 Global Energy efficiency

Energy efficiency is the major issue for the design of exascale HPC systems design. Although, this theme is an essential motivation in all system components development (Compute processors, memory, storage, interconnect...), the global system budget must be checked and balanced to provide good system performance for all HPC applications. The successive milestones, as specified in the first version of the SRA (100, 45 and 20kW/Pflops), should be reassessed. As technological difficulties arise, they are being delayed. The first 100kW/Pflops milestone at the end of 2015 is now expected to be met in mid-2016. The intermediate 45kW/PFlops in 2018 is now seen as being very challenging. There could be two intermediate steps before reaching 20KW/Pflops in 2022/2023, with possibly 60kW/Pflops in 2018 and 35kW/Pflops in 2020. [M-ARCH-7]

#### 5.1.5 Virtualisation

Virtualisation is an important tool for improving HPC systems ease-of-use, reliability and security. At the node level, containers can be set-up to facilitate system administration. Containers will provide a flexible way to tailor the run-time environment for each user and application. They will also enforce better security as applications will be insulated from system software and other applications running on the system.

In the network, virtualisation will allow for a good Quality of Service (QoS). It will arbitrate between concurrent users, applications and data flows and their respective priorities. Another important aspect is that it could help improve system resiliency with an easier implementation of Check-Point/Restart at the system level.

It is necessary to develop virtualisation at all levels of the HPC systems and in a coherent way. [M-ARCH-8]

#### 5.1.6 New application domains

High Performance Data Analysis (HPDA) is a good example of new application domains which could benefit from the HPC experience. HPDA applications have emerged in recent years and have been, so far, mostly based on the Map-Reduce distributed algorithm. New classes of problems are now requiring more sophisticated approaches (e.g. graph analysis and real-time analysis), and the necessary tools, HW, SW and development environment, are being investigated. There seems to be a lot in common with HPC as these new algorithms require a much tighter programming environment. HPDA could make use of HPC technology. And HPC architecture could take into account HPDA specificities. [M-BDUM-DIFFUSIVE-1]

#### 5.1.7 New disruptive HPC architectures

Besides HPC accelerators (GPUs, Many-cores...), other types of processing elements such as FPGAs, DSPs... have also been proposed for various dedicated applications. They seem well suited for in-flight data processing. However, the specificities of their programming model have so far limited their adoption. The situation must be reassessed in light of the new developments underway, which integrate these devices more tightly with the rest of the system's resources. Ultimately, completely new architectures could be proposed for HPC systems in general or for important subsets of HPC applications. For example, Processor in Memory (PiM) has been suggested several times as a way to break the memory wall. A super-efficient interconnection network using photonics, for example, could completely change the way the system's resources (processors/memory/storage) are organised. [M-ARCH-10]

### 5.2 SYSTEM SOFTWARE AND MANAGEMENT

#### 5.2.1 Operating system

The purpose of an operating system is to manage efficiently the resources of a computer system and to bridge the gap between the physical resources that make up such a system and the abstract view of a system, which run-time systems and programming models require. For HPC systems, operating systems typically operate on each node independently, with co-ordination executed through higher layers of Cluster operating or management systems. Given the rapid change in resources and programming models, a basic operating system must be defined for the exascale community. A suitable abstraction and a common set of APIs implementing it will be defined and can be used by a run-time system to support the management of resources, including adaptive and dynamic management policies that identify and react to load imbalances and the intermittent loss of resources.

The node architectures in supercomputers are becoming more and more complex. Increasing levels of parallelism in multi- and many-core chips, complex memory hierarchies and emerging heterogeneity of computational resources, coupled with energy and memory constraints, force a re-evaluation of our approaches towards operating systems and run-time environments.

To enable optimal use of emerging HPC architectures, evolutionary improvement of existing operating systems should be explored.

- $\cdot$  Kernel scheduling policies must be designed and implemented which solve multithread contention [M-SYS-OS-1].

- New memory management policies and libraries for complex memory hierarchies need to be developed which enable applications to use these [M-SYS-OS-3].

- $\cdot$  Offload programming model support is needed for optimal use of heterogeneous architectures [M-SYS-OS-5].

$\cdot$  To avoid limitations in scalability, reliability issues and kernel overhead OS decomposition [M-SYS-OS-6], container or virtualisation usage [M-SYS-OS-4] should be explored.

The great challenge for future operating systems is mainly on interoperability with future run-time systems, middleware, and tools. The role of OS and run-time system interaction is critical to minimise power usage, improve fault tolerance and increase performance. The interfaces between the layers will have to be studied and clearly specified. Today, experimentation is spread in many small and incomplete research projects.

The low-level APIs exposed by the OS and the various services implemented by the run-time system must be seen in the context of their use by programming models and applications. The complex interactions between components do require a holistic view in order to achieve best scalability and performance – it is not possible to attain this by defining APIs and optimising components in isolation.

System security support is a horizontal critical topic which needs to be accommodated at each significant hardware or software evolution step. Today, most OS levels are mainly based on SE Linux, and it will be mandatory to investigate how to integrate existing and emerging security mechanisms with OSs suitable for HPC. This should take into account the HPC-specific security requirements [M-SYS-OS-7].

Research topics:

- Offer a simple but efficient abstraction of the hardware to enhance the programming models,

- Define mechanisms to accommodate extended APIs and allow passing of hints from applications to the OS/RTS, e.g. for I/O and management of data and threads,

• Improve hardware abstraction for compilers and support new compiler features, e.g. optimisation and parallelism extraction,

• Extend run-time systems by developing mechanisms for passing hints from applications and new algorithms for better managing data locality, scheduling, I/O, coherency, etc.,

• Provide programming model developers with an efficient API for run-time services,

• Revisit APIs to support inter- and intra-node communication, thread management, and explicit management of the memory hierarchy provided by the entire system,

• APIs to support energy monitoring, management and resiliency will be essential (see also Chapter 5.4 and milestones M-ENR-MS-1 and M-ENR-MS-2 in Chapter 6.4),

• Fault tolerant/masking strategies for collective OS services are indispensable,

• Remove scalability limitations (such as OS Jitter) inherent in current operating systems by de-constructing their implementations, and leveraging concepts such as dedicating system resources to application and various OS functions,

• Hypervisor, Virtualisation and container support at HW and system level;

· Offload programming support at OS level.

#### Expected results:

Capabilities to build different operating system instances and run-time systems, adapted to the needs of applications and programming models with respect to emerging exascale hardware, e.g. heterogeneous compute elements, complex memory hierarchies, use of accelerator embedded cores, etc.

#### 5.2.2 Interconnect management

Interconnect topology management and routing is expected to react on message requests from applications or I/O in real-time and create optimal traffic patterns. First, this challenge has an impact on routing algorithms which will need to become dynamic. Secondly, optimising and scaling of application requests will require leveraging low-level communication acceleration based on hardware [M-SYS-IC-1]. A new borderline between low-level system control and application execution in user space on top of interconnect interfaces needs to be specified.

Identifying and fixing congestion situations and trouble-shooting errors [M-SYS-IC-2] of these networks is a real challenge that will require new management solutions to be developed.

At the interconnect adapter-level, driver and low-level interfaces will evolve depending on hardware technology (in particular closer integration of adapters and nodes) and on new programming model needs. Here, a tight cooperation between system software developers, system architects, and programming model designers will be necessary to integrate new low-level protocol capabilities and define a well-adapted API for higher levels of programming software.

The support of a virtualisation environment over the entire HPC infrastructure is a new issue. Low level support of virtualisation, such as the definition of virtualised networks is currently not fully supported.

Exascale interconnects are mainly performance driven, but it could be interesting to explore how to keep performance capabilities and develop compliance with virtualisation requirements e.g. for QOS routing or security purposes [M-SYS-IC-3].

· Adaptive and dynamic routing algorithms,

· OS-bypass and new low-level hardware interface API [M-SYS-IC-1],

$\cdot$  Congestion control and concurrent access regulation [M-SYS-IC-2],

· Scalable interconnect management tools,

• Intra-node and inter-node network low-level operation and addressing model;

$\cdot$  Network virtualisation support or compliance [M-SYS-IC-3].

#### 5.2.3 Cluster management software

Maintaining a clear view of the configuration and status of HPC systems is indispensable as they are exceedingly complex and susceptible to small perturbations that can have an extraordinary impact on performance, consistency and usability.

Today's ability to manage and scale to tens of thousands of nodes is solved by innovative cluster management frameworks. The new challenge of cluster management is driven much more by the multiplicity of applications execution contexts and by the flexibility required for I/O and data space management. Virtualisation and containerisations become a way to define specific and secure execution contexts. Cluster management, whatever the size of supercomputer, needs to integrate the management of this new environment.

#### Research topics:

• Flexible execution context configuration and management: The variety of hardware, programming environment, and applications' requirements will demand new tools to compose, integrate and store system images, containers definitions or virtual machines [M-SYS-CL-1],

• "Real-time" failure diagnostics and prescriptive maintenance based on Big Data analytics technics [M-SYS-CL-2],

• System security: system management also has to ensure system integrity, a major factor of which is system security [M-SYS-CL-3],

• Performance counters: design and implement performance counter APIs that provide scalable access to sufficiently detailed and up-to-date information for exascale performance analysis tools (see also M-ENR-MS-1 in Chapter 6.4)

#### Expected results:

A complete and consistent framework, which offers strong integration and configuration capabilities and powerful supervision tools.

#### 5.2.4 Resource management and job scheduling

Resource management and job scheduling are a critical function for efficient use of Big Data infrastructures and HPC systems. New mechanisms or improvements of existing ones will be necessary to reach: a sufficient level of scalability, the objectives of efficient utilisation of system resources and energy, reliable fulfilment of application SLAs; and, highest allocation flexibility. These have to be tightly coupled with applications and software environment deployment requirements (such as co-scheduling of coupled applications) and should take new allocation criteria into account, whilst collecting fine-grained information on job execution context.

#### Research topics:

Centralised control will not be able, from now on, to scale up and manage the complexity of scheduling and orchestrating modern large-scale application workflows.

Resources heterogeneity and the multiplicity of resource-selection criteria such as power consumption, or data locality are real challenges for an exascale resources manager.

With the extreme data focus, the role of data handling and heterogeneity is more and more critical on supercomputers (see M-SYS-RM-2). Data locality becomes a critical parameter in allocation criteria so that data-aware scheduling is necessary (see also Chapter 5.3). Scheduling needs to be data-aware but also tightly coupled with data movement from storage to memory.

During execution, the interaction between the job resource allocator and the run-time will be a key factor for performance and reliability of application execution. These dynamic capabilities require evolutionary improvements of job scheduling and resource manager.

With uptake of virtualisation and containerisation, the application's execution context becomes specific to each task. Next generation resource schedulers will need to support efficient deployment of this specific software environment prior to the execution of applications. There is also the requirement for elasticity (adding/removing resources to/from running jobs), migration and offload to a cloud. So, new workflow scheduling models and resource allocation policies need to be architected and developed.

Multi-objective adaptive scheduling in a dynamic environment [M-SYS-RM2] will probably be a way to deal with most of the above issues. However, the complexity of the scheduling will be enormous and its scalability will be a tough challenge.

Scheduling is also impacted by cross-layer issues such as energy efficiency, resiliency and security. In particular, since energy usage and power control mechanisms are themselves highly dynamic and application-dependent, adaptive scheduling has a high potential to help with the energy challenge (see also Chapter 5.4 and M-ENR-MS-2 in Chapter 6.4).

For a highly interactive use of HPC systems, job pre-emption is desirable. In this way users could get access to the resources when they need them, rather than when the scheduler provides them. To be of value, this feature will require efficiency in suspend-and-resume job support.

Exascale systems require a failure-tolerant application environment, implementing at least effective checkpoint/restart features [M-SYS-RM-3 and M-ENR-FT-6 and M-ENR-AR-4]. The system software layers will need to provide the required basic mechanisms for storing, managing and retrieving state, in close collaboration with the I/O subsystem. Extensions of such mechanisms could support the emerging use case of highly interactive access to HPC resources.

#### Expected results:

Dynamic resource allocation capabilities and powerful multi-criteria scheduling algorithms.

#### 5.2.5 Visualisation software

Current and future supercomputers enable numerical simulations of unprecedented fidelity and scale. The petabytes and soon exabytes of data produced by these simulations are increasingly difficult to analyse. Powerful tools are, therefore, required to analyse and interactively visualise data without - mainly for energy efficiency reasons - moving it over the HPC interconnect fabric or copying it in memory.

Specific requirements are:

• Visualisation performance must scale directly with the simulation performance, allowing for simulations at unprecedented scale and with previously unattainable visualisation accuracy,

· Location of simulation and visualisation minimises data movement and enables efficient workflow execution, reduced time to solution and overall system power efficiency,

• Flexibility of use of compute and visualisation resources supports dynamic scheduling,

· Global shared access infrastructure (i.e. network, storage, resource scheduling) is provided;

• On-the-fly analysis, often referred to as "in-situ visualisation" [M-SYS-Vis-1] or "in-situ analysis" is supported in an efficient way, enabling the emerging interactive supercomputing use case.

Today, visualisation and analytics in HPC is dominated by the open source tools Paraview and VisIt, both funded by the US DOE. Both were started more than a decade ago. Whether the requirements for visualisation can be better achieved by evolving these or by creating entirely new frameworks will remain to be seen.

#### Research topics: